2021年01月20日 公開

2025年 01月31日 更新

半導体の微細化に関して、第1回では半導体の大きなトレンドであるムーアの法則と微細化について第2回では半導体プロセスと微細化のキープロセスであるリソグラフィについて説明しました。今回は、実際に微細化がどのように進んできたのかをお話ししましょう。

第3回 半導体の微細化と国際半導体技術ロードマップ

半導体の微細化とプロセス名

半導体のプロセスは、例えば0.18μmプロセスというように、寸法で呼ばれます。この場合、一般的には(あるいは慣習的には)、0.18μmというのが、このプロセスでの最小寸法でトランジスタのゲート電極と呼ばれる部分の線幅(ゲート長)を表しています(少なくとも我々はそう思っていました)。0.18μmの次の世代が0.13μmですが、0.13÷0.18=0.72なので約0.7倍に縮小されています。面積にすると0.7 x 0.7=0.49で約半分になり、よって一世代進むと素子の密度は2倍になります。半導体プロセスというのは、このような形で2~3年くらいで次の世代(前世代の約0.7倍に縮小)に進むということを繰り返してきました。実際の例を挙げると、・・0.5μm→0.35μm→0.25μm→0.18μm→0.13μm→90nm→65nm・・(1990年代から2000年代頃)という感じです。

|

※μmとnm:μm(マイクロメーター)は10-6メーターすなわち100万分の1メーター、 nm(ナノメーター)は10-9メーターすなわち10億分の1メーター、例えば0.18μm=180nm

※プロセス名の「○○μm」や「○○nm」という数字のことをプロセスルールと呼ぶことも多いです。 |

上に述べたように、以前のプロセス名はほぼそのプロセスの最小寸法(トランジスタのゲート電極の線幅(ゲート長))を表すものでした。私の経験した範囲では、65nmまでは概ねその通りだったと思います。概ねと書いたのは、例えば65nmプロセスの最小寸法が60nmだったとか、その程度の違いはあったということです。しかしその後、(私は65nmの次すなわち45nm以降は実際に経験していないのであくまで聞いた話になりますが)トランジスタの構造を変えずに同じトレンドで単純に小さくすることがだんだん困難になってきたようです。その困難を克服するために色々な技術が導入されてきましたが、トランジスタの構造が従来の平面構造(二次元)のままではトレンドを維持できなくなり最先端のトランジスタは立体構造(三次元)になっています。

実際に最先端の立体構造のトランジスタと最先端のEUV露光技術を採用している現時点(2025年初頭)での最先端プロセス(7nmや5nmや3nm)のゲート電極の線幅(ゲート長)は10nm以上あるようです。プロセス名と実態が完全に乖離してしまっていますね。1990年代に現役でプロセス開発をしていたような技術者にこのことを話すと、びっくりする人も多いと思います。プロセス名の数字は一体何なのか?と思ってしまいます。

2010年代後半から2020年頃にかけて、それまで微細化レースをリードしていたはずのインテルが10nmや7nmというその当時の最先端の微細プロセスで苦戦しているという話がニュースになりました。当時TSMCとサムスンは7nmを量産し5nmの量産も始まろうとしていましたので、インテルが遅れているようにも思えましたが、インテルによればインテルの10nmは他社の7nmと同等ということでしたし、私もネットで収集できる様々な情報や分析を見ましたがインテルの10nmは他社の7nm相当だと思いました。この例を見ても、最先端の微細プロセスでは、このプロセス名の数字だけを単純に比較すること自体に意味がなくなっています。

その後インテルはプロセスの呼称を変えています。従来10nm Enhanced SuperFinと呼んでいたものをIntel7という呼称に変えています。他社の7nm相当であることを示していると思われます。TSMCとサムスンも同様にプロセス名からnmという表示をなくしています。たとえば2025年の初頭の時点で量産されている最先端プロセス(従来3nmと呼ばれていたプロセス)の呼称をTSMCはN3、インテルはIntel3、サムスンはSF3と呼称しています(ただし今までの表記と併記されている場合も多いです)。ただ、呼称に出てくる数字は現実のデバイスのパターンの寸法とは直接リンクしていないので、数字が同じであれば同等のプロセスであるとは言えず、結局中身を見てみないとわからないというのが実態です。

| ※私の経験した範囲は、一般的なロジック製品向けのプロセスやアナログ混載ロジック製品向けのプロセスですので、上の話もそれがベースになっています。実際はプロセッサやメモリ等の製品分野ごとに要求事項が異なり、それぞれのプロセスは独自の進化をするようになっています。プロセッサ用のプロセスでは同じプロセス世代でもゲート長は一般的なロジックプロセスよりも細かったようです。 |

国際半導体技術ロードマップ(ITRS)

ムーアの法則を実現すべく前節で述べたような形で微細化が進んで来たわけですが、それを具体的に示した技術ロードマップが作られていました。最初のロードマップはSIA(Semiconductor Industry Association米国半導体工業会)が作成したNTRS(National Technology Roadmap for Semiconductors)の1992 年版ですが、1998年版からは欧州、日本、韓国、台湾の業界団体も参加してITRS(International Technology Roadmap for Semiconductors)という国際的なロードマップが作られるようになりました。奇数年に全面改訂版、偶数年に部分改訂版が発行されてきましたが、2015年版が最後になりました。

ロードマップにはどういう役割があったのでしょうか?半導体の微細化を進めるのは半導体デバイスメーカーだけではできません。製造装置や各種材料は、製造装置メーカーや材料メーカーが作っていますので、デバイス、製造装置、材料のそれぞれのメーカー間の協力が不可欠です。また、デバイスメーカーごとに全く違う装置や材料を開発することも現実的ではないでしょう。デバイス、装置、材料それぞれのメーカーを含めた業界全体として、共通の部分はある程度足並みをそろえる必要があり、ロードマップというものに意味があったのではないでしょうか。

実際にITRSには「過去30年で必要投資額はますます増大したために、産業内での協力が進展し、多くの企業間研究開発協力、コンソーシアム、その他の協力ベンチャ企業が生み出されている。このような研究開発プログラムをガイドする一助として」編纂を開始したと記載されています(ITRS 2011 Edition(JEITA訳) Executive Summary P.1)。また「ロードマップは、本質的には、「産業界がムーアの法則やその他のトレンドを維持するためには、どのような技術的な力を開発しなければならないか?」というチャレンジ精神に基づいてまとめられたものである」と書かれており、ムーアの法則を維持することを前提として作成されていることがわかります(ITRS 2011 Edition(JEITA訳)Executive Summary P.2)。

ITRSはムーアの法則を維持するための15年先までのロードマップを示してきましたが、その期間内に微細化が行き詰まる可能性が高くなったことから、2015年版は従来のムーアの法則を具現化するためのITRSではなく、半導体の応用分野を議論の起点とする新方針のもとで作成され「ITRS2.0」として公表されました。しかし「ITRS2.0」はこの2015年版が初版でかつ最終版となり、より範囲を広げたIRDS(International Roadmap for Devices and Systems)という新たな活動に引き継がれました。

ITRSのレポートはSIA(Semiconductor Industry Association)のWebsite(https://www.semiconductors.org/)でITRSと入力して検索すると閲覧およびダウンロードができます(2025年1月時点)。日本語訳はJEITAの半導体技術ロードマップ専門委員会のサイト(http://semicon.jeita.or.jp/STRJ/index.html)で2026年3月末まで閲覧およびダウンロードができるようです。ITRSの活動を引き継いだIRDSの同様のレポートはIRDSのWebsite(https://irds.ieee.org/)のロードマップのページ(Roadmap - IEEE IRDS™)で閲覧とダウンロードができます。

※前節で述べたプロセス名と実態の乖離についてはIRDSレポートのExecutive Summaryにも記載があります。たとえば2023年版(International Roadmap for Devices and Systems (IRDS™) 2023 Edition - IEEE IRDS™)のExecutive Summaryの序論の1.2.2(P.24)をご参照ください。

ロードマップの例 ~リソグラフィ~

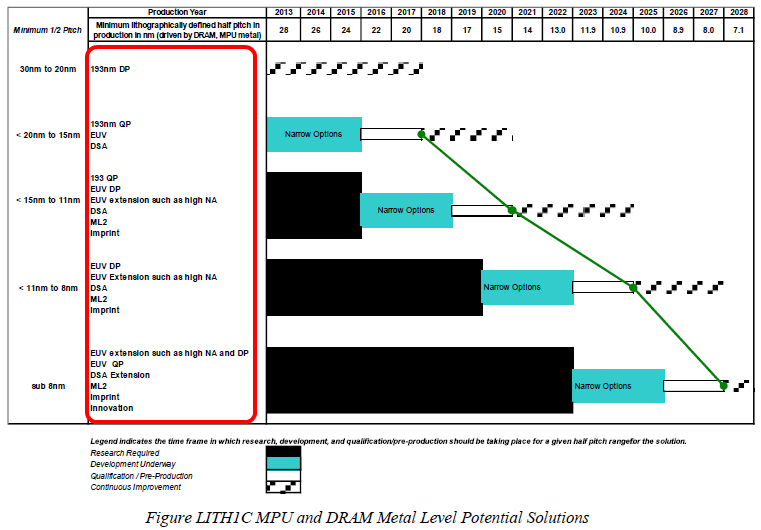

前回リソグラフィについてお話ししましたので、ITRS 2013年版からリソグラフィのロードマップの一例を以下に示します。

(ITRS 2013 Edition(JEITA訳)リソグラフィ P.7)

15年後の2028年までのロードマップとなっています。今後候補となる露光技術を記載している部分を赤枠で囲っておきました。一番上は量産中の技術で、193nmDPはArFエキシマレーザー193nmのダブルパターニングのことです。その下はさらに微細化が進んだ時の露光技術の候補をいくつかあげています。微細化が進むほど候補が増えています。QPと書かれているのはマルチパターニングの一種でクアドラプルパターニング(4重露光)の略です。2013年のロードマップでリストアップされた露光技術の候補の中で、ArFエキシマレーザー193nmのDPやQPの次に実用化されたのはEUVです。2010年代の末頃から最先端のロジック半導体製品の量産に適用されています。それ以外の候補の中で2025年の初頭の時点で実用化に近づいているのは、私が知る限りでは、imprintです。量産用の装置をキヤノンが2023年に発売しました。キオクシアでフラッシュメモリーへの量産適用を目指した検証が行われているということです。この技術を使った露光技術のことをナノインプリントリソグラフィ(略してNIL)と呼んでいます。それ以外のML2とDSAは、私の知る限り、少なくとも半導体の最先端微細プロセスの量産用としての実用化には至っていないと思います。ML2はMaskless Lithographyの略で電子線による直接描画のこと、DSAはDirected Self Assemblyの略で自己組織化リソグラフィと呼ばれるものです。

| ※Imprintはハンコを押すという意味の単語です。ナノインプリントリソグラフィは、光を使ってパターンを転写するのではなく、文字通りハンコを押すようにして微細パターンを形成する技術のことです。巨大で高額で電力消費の大きな装置を使うEUV露光に比べて、シンプルで低コストかつ低消費電力の技術です。キヤノン、キオクシア、DNPの3社が共同で開発を進めています。 |

| ※電子線による直接描画:マスクの回路パターンを転写するのではなく電子線でウェーハ上の感光材に直接回路パターンを描くもの。 1970年代から研究開発されている技術で、1970年代後半から1980年頃に光を使ったリソグラフィの限界が叫ばれたことがあり、有力な代替技術として電子線による直接描画が検討されていました。実際私が新人時代(1980年代前半)にこの電子線描画導入検討の担当をしていたことがあります。量産に使うにはスループットが低かったことと光露光技術が進歩したことでウェーハプロセスには使われませんでしたが、回路原版であるマスクのパターン形成に使われています。 |

以上、前回と今回は微細化に関連する技術的な側面についてお話してきましたが、次回はもう少しビジネス寄りのお話をしたいと思います。

※2025年01月31日、以下の部分の内容の更新を行いました。

1.「半導体の微細化とプロセス名」の第3パラグラフ以降を加筆・修正しました。

2.「国際半導体技術ロードマップ」の最終パラグラフを加筆・修正しました。URLリンクの見直しも行いました。

3.「ロードマップの例 ~リソグラフィ~」の後半部分をブログ公開以降の技術開発の進展を踏まえて加筆・修正しました。

※他の記事はこちら:

シリーズ:半導体の微細化

第1回: 半導体の微細化 ムーアの法則とは

第2回: 半導体の微細化と半導体プロセス

第3回: 半導体の微細化と国際半導体技術ロードマップ

第4回: 半導体の微細化と半導体ビジネス

第5回: 半導体の微細化と半導体ビジネス その2

第6回: 半導体の微細化と半導体デバイス

第7回: 半導体の微細化 スケーリング則とは

第8回: 半導体の微細化 スケーリング則の限界

第9回: 半導体の微細化とアナログ回路

シリーズ:Siウェーハの大口径化

第10回: Siウェーハの大口径化 ~ありふれた物質Si(シリコン)が主役になるまで~

第11回: Siウェーハの大口径化(その2) ~Siウェーハができるまで~

第12回: Siウェーハの大口径化(その3) ~大口径化の理由と歴史~

シリーズ:半導体産業の水平分業化

第13回: 半導体産業の水平分業化とファブレスの躍進

第14回: 半導体産業の水平分業化の歴史~ファブレス半導体企業の誕生~

第15回: 半導体産業の水平分業化の歴史~ファウンドリの誕生~

第16回: 半導体産業の水平分業化 ~ファウンドリは下請けか?~

第17回: 半導体産業の水平分業化 ~製品別、国別の水平分業の実態(前編)~

第18回: 半導体産業の水平分業化 ~製品別、国別の水平分業の実態(後編:国別)~

第19回: 半導体産業の微細化と水平分業化(番外編)~先端ロジック半導体の起源と定義と種類~

第20回: 先端ロジック半導体の仲間たち ~CPU、GPU、MPU、MCU、SoCとは~

第21回: 半導体産業の微細化と水平分業化(番外編)~チップレットとは~

Comment