前回はスケーリング則に則った微細化がデジタル回路に大きなメリットをもたらすというお話をしましたが、今回は、そんなうまい話が永遠に続くことはない、というお話です。

2021年09月16日 公開

2025年05月09日 更新

第8回 半導体の微細化 スケーリング則の限界

スケーリング則の限界

最初に前回の復習です。デジタル回路をスケーリング則に則って微細化した時のメリットを整理しておくと以下になります。

①高集積(集積度一定の場合はチップ面積縮小) ②高速 ③低消費電力

ただしこんなうまい話が永遠に続くことはありえず、(人によって解釈は異なるかもしれませんが)単純なスケーリング則が機能したのは2000年くらい、プロセス世代で言うと0.18μm(180nm)辺り、までだったと思います。

スケーリング則通りに微細化を進めていくと、デバイスの大きさや電源電圧がゼロに向かって小さくなっていくことになります。遅かれ早かれどこかで何かの限界が来ることは直感的には想像できると思います。

たとえば、スケーリングを進めて大きさがどんどん小さくなると、どこかで原子間距離や原子の大きさを下回ってしまいますが、そんなことは実際にはあり得ません。

二次元パターンの場合は、そこまで行く前に、第2回で説明したリソグラフィによるパターンの形成が非常に困難になります。長い開発期間を経てようやくEUV露光技術が実用化されたとお話ししましたが、その先が見えているのかどうか、私にも現時点で知見はありません。また、EUV露光装置は100億円以上するというお話を第5回でしましたが、一部の特別な企業を除く大部分の企業にとっては、経済的な限界を超えていると思います。

大きさのスケーリングの限界と電源電圧のスケーリングの限界について以下に少し詳しく説明しますが、電源電圧の限界を説明するにはリーク電流(漏れ電流)というものについて考える必要があります。

なので、まずリーク電流について説明しましょう。

リーク電流とは?

第6回で、MOSトランジスタはデジタル回路ではスイッチとして使われるということをお話ししました。スイッチはONしたときには電流が流れ、OFFしたときには電流が全く流れない(すなわちゼロ)というのが理想ですが、残念ながらMOSトランジスタはOFF時にもわずかながら電流が流れます。この電流のことをリーク電流(漏れ電流)と呼びます。

※OFF(オフ)時に流れる電流なので、オフ電流やオフリーク電流と呼ばれることもあります。

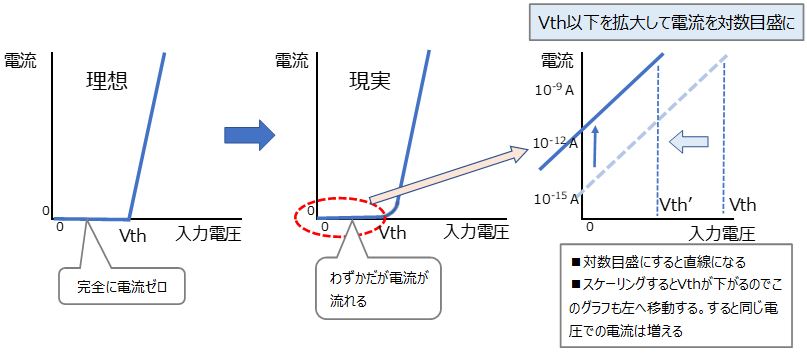

MOSトランジスタはある入力電圧を超えるとトランジスタがONし、大きな電流(オン電流)が流れるようになります。このONになる入力電圧をしきい値電圧(Vth)と呼びます。しきい値電圧(Vth)以下はOFF状態ですが、上で述べたようにリーク電流が流れます。リーク電流は、入力電圧をゼロVに向かって下げていくと指数関数的に減少し急激にゼロに近づきますが、完全なゼロになることはありません。

※Vth以下での電流は電圧に対して指数関数的に変化するので、電流を対数目盛にしてグラフを書くと直線になります(下図の一番右のグラフ)。しきい値電圧以下の電流なので、しきい値の英語であるスレッショルドを使ってサブスレッショルド電流あるいはサブスレッショルド・リーク電流とも言われます。

スケーリング則に従えば、このしきい値電圧(Vth)もスケーリングされて小さくなります。しかし、リーク電流の振る舞い、すなわちしきい値電圧(Vth)以下で入力電圧を変化させたときのリーク電流の増減の仕方(指数関数的変化)は、スケーリングとは関係ない物理的なメカニズムで大まかに決まってしまい、スケーリングしてもあまり変わりません。

従って、スケーリングしてしきい値電圧(Vth)を下げると、下の図の右端のグラフのように、入力電圧ゼロVの時のリーク電流は急激に増加します。MOSトランジスタは、入力電圧がしきい値電圧(Vth)以下になると電流を急激に減らそうと頑張るのですが、しきい値電圧(Vth)がスケーリングされて小さくなりゼロVに近づくと、電流を減らしきる前に入力電圧がゼロVになってしまうというわけです。

その結果、従来は入力電圧ゼロV時のリーク電流は無視してもよいくらい小さかったのですが、微細化(スケーリング)が進むといずれ無視できない大きさになることがわかると思います。

電源電圧のスケーリングの限界

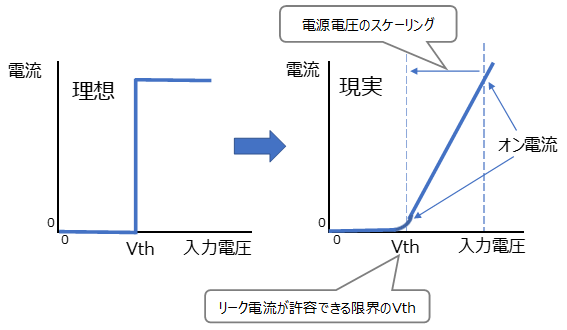

上で話した内容を簡単にまとめると、スケーリング則通りに微細化した場合、しきい値電圧(Vth)も下がるのですが、しきい値電圧(Vth)が下がるとリーク電流は指数関数的に急激に増加します。スケーリングを続けるとどこかでリーク電流が無視できないレベルになります。

それを避けるには電源電圧のスケーリングをある一定のレベルでやめるしかありません。

電源電圧はスケーリングしてもしきい値電圧(Vth)はスケーリングしない、すなわち電源電圧を下げてもしきい値電圧(Vth)を下げなければいいんじゃないの?と思われる方がいらっしゃるかもしれません。

実際それは可能です。しかしそうすると、リーク電流は抑えられますが、ONしたときの電流が上がらなくなってしまうんです。

ON、すなわち入力電圧がしきい値電圧(Vth)を超えた瞬間に一気に電流が流れればいいのですが、実際は徐々にある傾きを持って電流が増えていきます。入力電圧の最大値は電源電圧なので、しきい値電圧(Vth)と電源電圧の差がなくなると、電流が上がり切らないうちに電源電圧に達してしまいます。

たとえ仮にしきい値電圧(Vth)をリーク電流が許容できるレベルに保ったとしても、電源電圧のスケーリングを続けるといずれそのしきい値電圧(Vth)を下回ってしまいますので、限界が来ることには変わりはありません。

私の経験した範囲では、各プロセス世代の電源電圧は、0.35μm(350nm)プロセスでは3.3V、0.18μm(180nm)プロセスでは1.8V、0.13μm(130nm)プロセスでは1.2Vとスケーリングされています。しかし90nmプロセスでも1.2V、65nmプロセスでも1.2Vでスケーリングされていません。スケーリングされるなら65nmの場合は0.65V程度のはずです。2021年時点での最先端のプロセスは5nmですが、プロセスの数字通りにスケーリングされていたとすると0.05V程度になります。いくら何でもこれはなさそうな数字ですね。

第3回でお話ししたIRDS※のロードマップの2023Updateを見ると、ロジックデバイスの電源電圧は2023年で0.70Vですが2037年でも0.60Vとなっています。ロードマップ通りに行っても電源電圧の低下はあまり進まず、0.60Vに下げることも非常に困難とされています。前回お話ししたように電源電圧もスケーリングされることが前提で「単位面積当たりの消費電力はスケーリングしても同じ」という結論になっていたので、電源電圧がスケーリングされないとこの結論はなりたたず、先端ロジック製品では消費電力(すなわち発熱)が非常に深刻な問題になります。

※IRDS:第3回でも説明しましたがInternational Roadmap for Devices and Systemsの略称です。上述の電源電圧のロードマップは2023Update(International Roadmap for Devices and Systems (IRDS™) 2023 Edition - IEEE IRDS™)のMore Moore( IRDS™ 2023: More Moore - IEEE IRDS™)のエクセルの表をご覧ください。

大きさのスケーリングの限界 ~ゲート酸化膜~

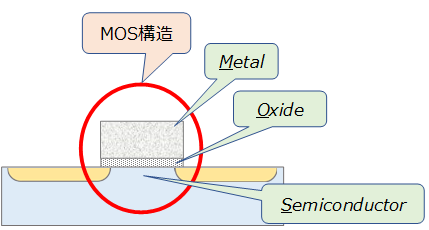

最初に話したように、物理的な寸法(大きさ)のスケーリングにも限界が出てきます。MOSトランジスタのゲート酸化膜(下図のOxide、Siの酸化膜)の厚さもスケーリングされますが、元々が薄かったこともあり最初に限界に到達しました。

0.35μm(350nm)プロセスで既に10nmかそれ以下でしたので、単純にスケーリングすると10nmプロセスでは0.3nmという原子間距離や原子の大きさ程度というあり得ない薄さになりますが、それ以前の段階(45nmプロセス辺り)で既に薄すぎてマクロな「絶縁膜」としての性質を失ってしまいます。すなわち絶縁できずにリーク電流が流れるようになり、そのままでは使えません。

物理的な寸法(大きさ)のスケーリングという点でも単純なスケーリングが破綻します。

限界を乗り越えるために

第3回で、最先端の微細プロセスではプロセス名の数字(10nm, 7nm, 5nm等)と実態が乖離していると書きましたが、今回の話を踏まえて言うと、単純なデナードのスケーリング則が適用できなくなったにも関わらずプロセス名の数字だけはスケーリングを続けている、と言えると思います。

ただ単純なデナードのスケーリング則は適用できなくなりましたが、新しい材料・技術を適用したりトランジスタを3次元化したりして高性能化を図ってきました。第3回でお話ししたITRSではこのことを等価的スケーリング(Equivalent Scaling)と呼んでいました。

例えば先ほどお話ししたゲート酸化膜の場合は、専門的な説明になりますが、誘電率の高い材料(High-k材料と呼んでいる)を使えばより厚い膜で電気的に同等の効果を出せるので、誘電率の高い新しい材料を採用しました。また、今まで説明してきたような平面構造(二次元)のMOSトランジスタでは微細化することが困難になり、22nm辺りからトランジスタは立体構造(三次元)になっています。

以上今回はデナードのスケーリング則の限界について説明しました。前回と今回でデジタル回路の微細化(スケーリング)について説明しましたが、次回アナログ回路と微細化のお話をして微細化シリーズを終わりにしたいと思います。

2025年05月09日

「電源電圧のスケーリングの限界」の節の最後に関連する話題を追加しました。

※その他の記事はこちら:

シリーズ:半導体の微細化

第1回: 半導体の微細化 ムーアの法則とは

第2回: 半導体の微細化と半導体プロセス

第3回: 半導体の微細化と国際半導体技術ロードマップ

第4回: 半導体の微細化と半導体ビジネス

第5回: 半導体の微細化と半導体ビジネス その2

第6回: 半導体の微細化と半導体デバイス

第7回: 半導体の微細化 スケーリング則とは

第8回: 半導体の微細化 スケーリング則の限界

第9回: 半導体の微細化とアナログ回路

シリーズ:Siウェーハの大口径化

第10回: Siウェーハの大口径化 ~ありふれた物質Si(シリコン)が主役になるまで~

第11回: Siウェーハの大口径化(その2) ~Siウェーハができるまで~

第12回: Siウェーハの大口径化(その3) ~大口径化の理由と歴史~

シリーズ:半導体産業の水平分業化

第13回: 半導体産業の水平分業化とファブレスの躍進

第14回: 半導体産業の水平分業化の歴史~ファブレス半導体企業の誕生~

第15回: 半導体産業の水平分業化の歴史~ファウンドリの誕生~

第16回: 半導体産業の水平分業化 ~ファウンドリは下請けか?~

第17回: 半導体産業の水平分業化 ~製品別、国別の水平分業の実態(前編)~

第18回: 半導体産業の水平分業化 ~製品別、国別の水平分業の実態(後編:国別)~

第19回: 半導体産業の微細化と水平分業化(番外編)~先端ロジック半導体の起源と定義と種類~

第20回: 先端ロジック半導体の仲間たち ~CPU、GPU、MPU、MCU、SoCとは~

第21回: 半導体産業の微細化と水平分業化(番外編)~チップレットとは~

Comment